### Jordan Journal of Physics

### **ARTICLE**

# Optimization of Source Pocket Height on Source Pocket Half Hetero Dielectric Double Gate TFETs (SP-HHD-DG-TFET)

Bed P. Pandey<sup>a</sup>, Santosh K. Pandit<sup>a</sup>, Sanju Shrestha<sup>a</sup>, Kavindra K. Kavi<sup>b</sup> and Om Prakash Niraula<sup>a</sup>

$^a\ Central\ Department\ of\ Physics,\ Tribhuvan\ University,\ Kiritipur,\ Kathmandu,\ Nepal.$

### Doi: https://doi.org/10.47011/18.4.7

Received on: 26/06/2024; Accepted on: 06/01/2025

**Abstract:** Tunnel field effect transistor (TFET) has attracted significant attention due to its extremely low sub-threshold swing (SS) and leakage current. However, due to the ambipolar effect and relatively low ON-current, researchers are modifying the structures and selecting appropriate materials. In order to increase the ON-current, a highly dense thin layer, source pocket (SP) is used, while a hetero-dielectric gate is used to reduce ambipolar current. Hence, various characteristics, properties, and parameters of the source pocket half hetero-dielectric double gate TFET (SP-HHD-DG-TFET) are studied by varying the SP height (4, 6, and 8 nm) using the Silvaco TCAD simulator. The optimized SP height of 6 nm shows a current ratio ( $I_{\rm ON}/I_{\rm OFF}$ ) and a sub-threshold swing (SS) to be 3.90 × 10<sup>12</sup> and 17.59 mV/decade, respectively. Hence, the optimized height and the model are suggested to be useful for low-power and high-speed devices.

**Keywords:** Sub-threshold Swing (SS), Conductance, Source Pocket (SP), Tunneling, Offcurrent, On-current, Tunnel field-effect transistor (TFET).

### 1. Introduction

The tunnel field effect transistor (TFET) is replacing conventional MOSFET due to its small sub-threshold swing (SS), less than 60 mV/ decade [1], and low leakage current. Hence, it can be used for low-current and low-power circuits [2]. However, a major disadvantage is the ambipolar current effect, where the n-channel TFET behaves as an 'ON' state instead of an 'OFF' state when a high negative gate bias voltage is applied. Hence, it became difficult to use TFETs in CMOS circuit applications. To address this challenge, various techniques have been explored, such as gate engineering, drain engineering, and spacer/ energy-band engineering.

The 'OFF' state tunneling current is controlled by using an additional gate, called a tunneling gate [3], in the gate engineering technique. Alternatively, using an underlap gate-

drain (UGD) in TFETs [2, 4] allows control of channel resistance near the drain channel current. However, both techniques require an additional gate or extra area near the drain. It limits the scalability of the device [5-7]. These challenges of scalability and tunneling current can be overcome by drain engineering, which involves using an undoped (UD) [5, 8, 9] or lightly doped (LD) drain, or introducing a pocket near the drain [10–13]. For instance, Dhiman *et al.* proposed a graded-doped (GD) drain TFET to mitigate the ambipolar effect [14].

On the other hand, Lu et al. [15] mentioned that due to the large and indirect bandgap of Si, Si-TFETs suffer from unacceptably low 'ON'-state currents, below the levels recommended by the International Technology Roadmap for Semiconductors (ITRS) [16,17]. The low 'ON'-current limits the switching speed of the device.

Corresponding Author: Sanju Shrestha Email: sanju.shrestha@cdp.tu.edu.np

Electronics and Communication Engineering Department, Motilal Nehru National Institute of Technology Allahabad, Prayagraj 211004, India.

To overcome this, the use of Heterojunction TFETs (HTFETs), formed by junctions between III–V semiconductors and silicon, has been suggested. For p-channel TFETs, the InAs/Si HTFET has been proposed because of its lower tunneling mass [18], which facilitates the direct tunneling process [19]. The 'ON'-state current can be improved by inserting an ultra-thin doping pocket at the junction between the heavily doped source and the intrinsic channel within the channel region [20, 21], as there will be the formation of steeper energy band bending and a reduction in the tunneling distance.

Energy-band engineering, i.e., using heterojunctions and the novel device structures of source pocket (SP), as done in the drain engineering, is used in a single device, specifically the InAs/Si heterojunction. The use of SP and junction, i.e., the hetero SP-TFET (HSP-TFET), is proposed by Lu *et al.* [15]. The authors have done comparative studies with traditional Si-TFETs and found that the proposed InAs/Si HSP-TFET significantly enhanced device performance.

Instead of using a single gate oxides of Si/Hf, horizontally stacked layers of high-k gate oxides have been shown to enhance multiple device characteristics. The decrease in the ambipolar current, along with SS values to below 5 mV/decade, is found by using SP along with a layer of high-k oxide materials in the gate [22]. Even the current switching ratio ( $I_{\rm ON}/I_{\rm OFF}$ ) is improved by varying the concentrations of doping and the height of the SP. Wang proposes that the hetero-gate-dielectric (HGD) and SP in a DG TFET enhance  $I_{\rm ON}$  and reduce the ambipolar current [23].

Sharma et al. showed that an SP of SiGe with oxides gives better electrical hetero characteristics compared to that of normal TFETs,  $SiO_2$ -gate oxide TFETs, high-k TFETs, and hetero-dielectric SP TFETs [24]. Kavindra et al. [25] also showed that the performance of SP hetero-dielectric double gate TFET (SP-HD-DG-TFET) is found to be better in terms of I-V characteristics, I<sub>ON</sub>/I<sub>OFF</sub>, and SS compared with hetero-dielectric double gate TFETs (HD-DG-TFET), high-k TFETs, and conventional DG TFETs.

Using Silvaco TCAD [26], various characteristics of the SP-half hetero-dielectric double gate TFET (SP-HHD- DG-TFET) were studied by varying the SP height. The optimized SP height significantly improves the device's properties, making it suitable for low-power, high-speed applications.

## 2. Device Structure, Parameters, and Simulation Details

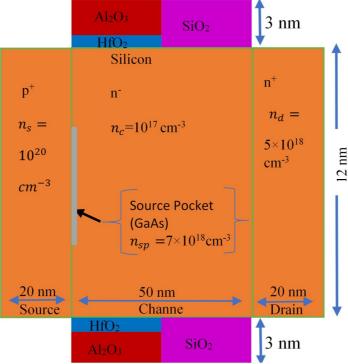

The 2D schematic diagram of the SP-HHD-DG-TFET is shown in Fig. 1. The gate consists of SiO<sub>2</sub> oxide in the half region near the n-doped drain, while the other half—toward the heavily p-doped source—uses hetero high-k dielectrics, specifically HfO2 and Al2O3. Since the gate structure is present on both the top and bottom sides of the channel, the device operates as a double-gate structure, which enhances channel controllability. The channel is composed of intrinsic Si, and a single, highly doped GaAs SP is introduced at the source-channel junction within the channel region. The various physical parameters used in the model are provided in Fig. 1 and summarized in Table 1. All simulations were performed using the Silvaco TCAD tool [26].

| TABLE | 1. | Constant | paramet | ers | used | tor | sımul | atıon. |

|-------|----|----------|---------|-----|------|-----|-------|--------|

|-------|----|----------|---------|-----|------|-----|-------|--------|

| Doping Concentration (cm <sup>-3</sup> ) |                    |  |  |  |

|------------------------------------------|--------------------|--|--|--|

| p-type Source (n <sub>s</sub> )          | $1 \times 10^{20}$ |  |  |  |

| n-type Channel (n <sub>c</sub> )         | $1 \times 10^{17}$ |  |  |  |

| n-type Drain (n <sub>d</sub> )           | $5 \times 10^{18}$ |  |  |  |

| $n$ -type SP $(n_{SP})$                  | $7 \times 10^{18}$ |  |  |  |

| Dielectric Constant                      |                    |  |  |  |

| SiO <sub>2</sub>                         | 3.9                |  |  |  |

| $HfO_2$                                  | 25                 |  |  |  |

| $Al_2O_3$                                | 8.5                |  |  |  |

| Length of the SP (nm)                    | 2.5                |  |  |  |

| Work function of gate (eV)               | 4.2                |  |  |  |

FIG. 1. Schematic cross-sectional view of the SP-HHD-DG-TFET. The gate consists of  $SiO_2$  (3 nm in height) near the drain, and the other half with hetero-dielectrics of  $HfO_2$ -  $Al_2O_3$  (1 and 2 nm in height, respectively) is near the source. The p-type source and the n-type drain have concentrations of  $1\times10^{\circ}20$  cm<sup>-3</sup> and  $5\times10^{\circ}18$  cm<sup>-3</sup>, respectively. n-type SP of GaAs and the channel of Si are with concentrations of  $7\times10^{18}cm^{-3}$  and  $1\times10^{17}cm^{-3}$ , respectively.

### 3. Results and Discussion

The 2D simulated structure of SP-HHD-DG-TFET is shown in Fig. 1. The doping concentration of the heavily doped source  $p^+$  of 20 nm in length is  $10^{20} \text{ cm}^{-3}$ . The nearly intrinsic n-type channel has a doping concentration of 1017 cm-3 and a length of 50 nm. The n –type doping concentration of SP of GaAl (length 2.5 nm), positioned between the source and the channel, is  $7 \times 10^{18} \text{cm}^{-3}$ . The n-type drain has a doping concentration of  $5 \times 10^{18} \text{cm}^{-3}$  and a length of 20 nm. Work functions of the front gate (Fgate) and back gate (Bgate) are equal (4.2 eV). The gates are made common in the circuit connection, and the work function of the SP is 5.3 eV. All constant parameters are given in Table 1.

In order to optimize the performance of the device, the Silvaco TCAD [26] simulator is used to vary the height of the SP (4, 6, and 8 nm). The obtained simulated characteristics and properties, such as surface potential, electric field intensity, band energy, and the I-V characteristics, are given in Figs. 2, 3, 4, and 5, respectively. The calculated physical parameters of the simulation, such as V<sub>TH</sub>, I<sub>ON</sub>, I<sub>OFF</sub>,

$(I_{ON}/I_{OFF})$  ratio, SS, and trans-conductance  $(g_m)$ , are given in Table 2.

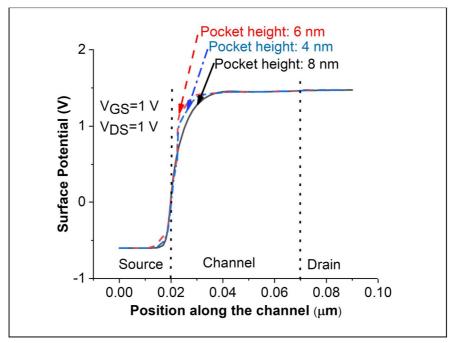

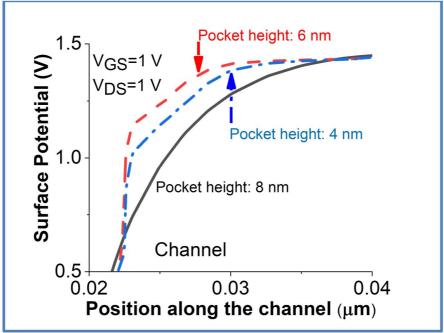

The variation of surface potential along the channel length at  $V_{GS} = V_{DS} = 1 \, V$  is shown in Fig. 2. A sharp increase in surface potential is observed at the source–channel junction. This enhancement occurs because the gate oxide near the source consists of high-k dielectrics (HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub>), and the heavily doped SP further strengthens the potential. Among the examined SP heights (4 nm, 6 nm, and 8 nm), the maximum surface potential is obtained for the SP height of 6 nm, as illustrated in the inset of Fig. 2.

In contrast, near and within the drain side of the channel, the effect of SP height is insignificant, and the surface potential remains nearly constant. This indicates that the region corresponds to the depletion or space-charge region. Kavi *et al.* [25] also included the drain–channel depletion region in their modeling to achieve accurate device representation in this area.

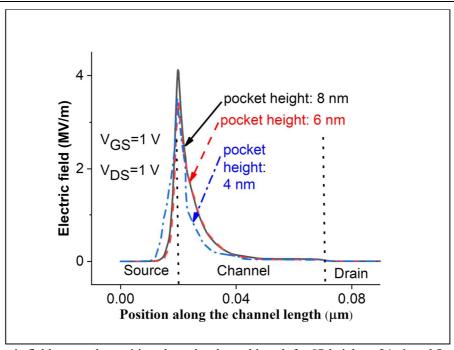

The electric field distribution, shown in Fig. 3, exhibits a strong peak at the source-channel interface. This is attributed to the high charge

carrier density in the source region as well as in the SP. The presence of high-k hetero-dielectrics (HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub>) at the gate near the source further contributes to the enhanced electric field. The maximum value at the sharp peak of the electric field is due to the presence of more charge for the SP of 8 nm in height. This peak indicates an increased number of charge carriers tunneling through the junction.

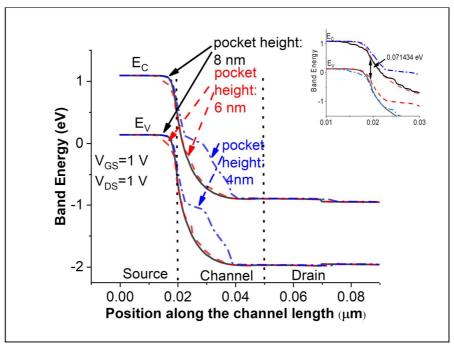

Figure 4 shows the state at  $V_{GS} = V_{DS} = 1 \text{ V}$ , i.e., at the 'ON' state. It is known that with n-type and p-type doping, the conduction band

energy level decreases and the valence band level increases, respectively, i.e., the Fermi level moves towards the conduction and valence band. Under the unbiased condition, the energy band is not sharp, representing the 'OFF' state. The energy gap increases due to the reverse biasing and becomes sharp, i.e., the higher level of the conduction band energy and the lower level of the valence band energy at the source and drain sides, respectively. will come very close to each other at the channel region due to the band bending. It can be seen in the inset of Fig. 4.

FIG. 2. Surface potential versus the position along the channel for SP heights of 4, 6, and 8 nm at  $V_{GS} = V_{DS} = 1 V$ . The inset view highlights the difference in the characteristics.

FIG. 3. Electric field versus the position along the channel length for SP heights of 4, 6, and 8 nm at  $V_{GS} = V_{DS} = 1 V$ .

FIG. 4. Band Energy variation versus the position along the channel length for SP heights of 4, 6, and 8 nm at  $V_{GS} = V_{DS} = 1 V$ .

At  $V_{GS}=0$ , the width of the tunneling channel and the height of the energy band are functions of the doping concentrations. Hence, electrons do not have enough energy to move from the valence band to the conduction band. Whereas, as  $V_{GS}$  increases, both the CB and the VB energy differences increase, as is the condition of –ve biasing/reverse bias. Figure 4 shows the energy band diagram under the condition  $V_{GS}=V_{DS}=1\ V$ , where the energy

varies along the effective channel length. With an increase in the gate voltage, more band bending takes place, i.e., the conduction band of the source and valence band of the channel/drain are increased and become sharper, causing a reduction in tunneling length, facilitating faster carrier movement in opposite directions across the source—channel junction, resulting in a higher drain current. At  $V_{DS} > V_{Th}$ , the electrons move from the valence band to the conduction band as

they have sufficient energy to tunnel. The interband tunneling is also due to the bands approaching each other, i.e., the narrowing of the effective length of the channel, corresponding to the ON-state condition. With an increase in the gate voltage, the current increases, as shown in Fig. 5. The inset view of Fig. 4 also shows the maximum narrowing of the effective channel length at  $V_{GS} = V_{DS} = 1 \text{ V}$ , causing such an effect. For the tunneling of the electron from the source to the drain via the channel region, the non-local band-to-band tunnel (BTBT) model is used [14, 27, 28]. Kavi et al. mentioned that to recombine the electron-hole pair during conduction through the channel, the Auger recombination and Shockley-Read-Hall recombination models are also used [22]. In addition, the Lombardi model is used to

incorporate the effect of doping, electric field, and concentration [22]. Due to the high concentration of doping in the source and drain, compared to that of the channel, the band gap narrowing (BGN) model is incorporated [29, 30]. Collectively, these physical models are included in the simulation to accurately describe the current tunneling phenomena.

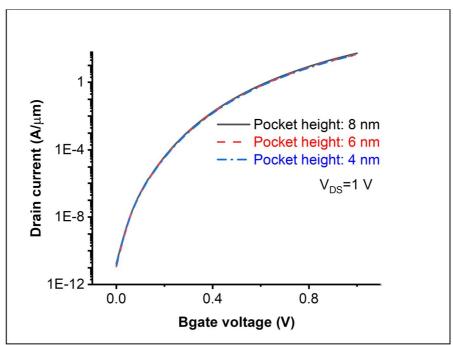

The variation of drain current versus reverse/back gate voltage for pocket heights ranging from 4 to 8 nm is given in Fig. 5 at  $V_{DS} = 1 \text{ V}$ . The drain current for the 8 nm pocket height is slightly higher than that for the rest of the heights, which is expected due to the availability of a larger number of carriers as the SP is heavily doped.

FIG. 5. Variation of drain current versus backward gate (Bgate) voltage for SP heights of 4, 6, and 8 nm at  $V_{DS} = 1 V$ .

TABLE 2. Physical parameters obtained by simulation with the height of the SP.

| S.N.  | Parameters -            | Height of the SP (nm)  |                        |                        |  |  |

|-------|-------------------------|------------------------|------------------------|------------------------|--|--|

| S.IN. | rarameters              | 8                      | 6                      | 4                      |  |  |

| 1.    | $V_{TH}(V)$             | 0.3465                 | 0.3446                 | 0.3445                 |  |  |

| 2.    | $I_{ON} (A/\mu m)$      | $5.20 \times 10^{-5}$  | $4.55 \times 10^{-5}$  | $4.31 \times 10^{-5}$  |  |  |

| 3.    | $I_{OFF}$ (A/ $\mu$ m)  | $1.78 \times 10^{-17}$ | $1.17 \times 10^{-17}$ | $1.48 \times 10^{-17}$ |  |  |

| 4.    | $I_{ON}/I_{OFF}$        | $2.93 \times 10^{12}$  | $3.90 \times 10^{12}$  | $2.91 \times 10^{12}$  |  |  |

| 5.    | Sub-threshold slope     | 53.62                  | 56.85                  | 54.31                  |  |  |

| 6.    | SS (mV/decade)          | 18.35                  | 17.59                  | 18.41                  |  |  |

| 7.    | g <sub>m</sub> (Siemen) | $3.39X10^{-4}$         | $2.93 \times 10^{-4}$  | $2.77 \times 10^{-4}$  |  |  |

The threshold voltage (V<sub>Th</sub>) does not vary significantly with the change in pocket height.  $I_{ON}$  decreases with a decrease in the height of the SP, whereas the I<sub>OFF</sub> decreases and then increases with the height of the SP. However, the current ratio is found to be maximum for the 6 nm height, with a value of  $3.90 \times 10^{12}$ . The current ratio is close to the p-channel SP-HD-DG-TFET, reported at  $4.4 \times 10^{12}$  by Kavi et al. [25]. The SS for the 6 nm SP height is 17.59 mV/decade and found to be the minimum when compared to that of the other heights. The trans-conductance g<sub>m</sub> for the height is also found to be lowest, i.e.,  $2.93 \times 10^{-4}$  S. So, the optimized height of the SP is expected to be appropriate for a low-power consumption application.

### 4. Conclusions

Due to the importance of using a SP along with the hetero-dielectrics of high-k materials in a DG-TFET, various electrical characteristics, such as surface potential, electrical energy,

bandgap energy, and I-V characteristics, are studied using Silvaco TCAD simulation software.

The calculations of threshold voltage, ON and OFF currents, current ratio, SS, and transconductance are also done.

The variation of such properties and parameters due to the height of the SP on the SP-HHD-DG-TFET is studied/obtained. The SP with the height of 6 nm is found to have the highest current ratio  $(I_{ON}/I_{OFF})$  and the lowest SS. Hence, the optimized height of 6 nm is recommended for low-power and high-frequency applications.

### Acknowledgment

The authors would like to acknowledge the Research Coordination and Development Council, Tribhuvan University, Kirtipur, Nepal, for the support provided through the National Priority Area Research Project: TU-NPAR-077/078-ERG-12.

### References

- [1] Wang, Q., Liu, H., Wang, S., and Chen, S., IEEE Trans. Nucl. Sci., 65 (8) (2018) 2250.

- [2] Nigam, K., Gupta, S., Pandey, S., Kondekar, P.N., and Sharma, D., Int. J. Electron., 105 (5) (2018) 806.

- [3] Saurabh, S. and Kumar, M.J., IEEE IEEE Trans. Electron Devices, 58 (2) (2011) 404.

- [4] Boucart, K. and Ionescu, A.M., IEEE Trans. Electron Devices,54 (7) (2007) 1725.

- [5] Garg, S. and Saurabh, S., Superl. Micros., 113 (2018) 261.

- [6] Upasana, Saxena, M., and Gupta, M., Micro Nanos., 163 (2022) 107147.

- [7] Pandey, C.K., Dash, D., and Chaudhury, S., Micro Nano Lett., 14 (1) (2019) 86.

- [8] Bagga, N., Chauhan, N., Gupta, D., and Dasgupta, S., IEEE Trans. Electron Devices, 66 (7) (2019) 3202.

- [9] Ahmad, S.A. and Alam, N., IET IET Circuits Devices Syst., 14 (3) (2020) 288.

- [10] Kumar, A. and Singh, S.S., In: 2016 Int. Conf. Commun. Signal Process. (ICCSP) IEEE (2016) 1448.

- [11] Kumar, A., Superl. Micro., 100 (2016) 1073.

- [12] Kumar, A., Superl. Micro., 100 (2016) 1143.

- [13] Zhang, M., Guo, Y., Zhang, J., Yao, J., and Chen, J., Nano. Res. Lett., 15 (1) (2020) 1.

- [14] Dhiman, P., Kavi, K.K., Ratnesh R.K., and Kumar, A., Int. Conf. Dev. Intell. Comput. Commun. Technol., (DICCT) (2023) 249.

- [15] Lu, H., Lu, B., Zhang, Y., Zhang, Y., and Lv, Z., Nanomaterials, 9 (2019) 181.

- [16] Noor, S.L., Safa, S., and Khan, Z.R., J. Comput. Electron., 15 (2016) 763.

- [17] Semiconductor Industry Association (SIA). International Technology Roadmap for Semiconductors 2015. Available online: https://www.semiconductors.org/wp-content/uploads/2018/06/6\_2015-ITRS-2.0-Beyond-CMOS.pdf (accessed on 1 February 2019).

- [18] Mookerjea, S., Krishnan, R., Datta, S., and Narayanan, V., IEEE Trans. Electron Devices, 56 (2009) 2092.

- [19] Das, G.D., Mishra, G.P., and Dash, S., Super. Microstr., 124 (2018) 131.

[20] Chang, H.Y., Adams, B., Chien, P.Y., Li, J., and Woo, J.C., IEEE Trans. Electron Devices, 60 (2013) 92.

- [21] Mahajan, A., Dash, D.K., Banerjee, P., and Sarkar, S.K., J. Mater. Eng. Perform., 27 (2018) 2693.

- [22] Kavi, K.K., Tripathi, S., Mishra, R.A., and Kumar, S., Silicon, 14 (2022) 10101.

- [24] Sharma, V., Kumar, S., Talukdar, J., Mummaneni, K., and Rawat, G., Mat. Sci. Sem. Pro., 143 (2022) 106541.

- [25] Kavi, K.K., Tripathi, S., Mishra, R.A., and Kumar, S., 02 August 2023, PREPRINT, Research Square, https://doi.org/10.21203/rs.3.rs-3189342/v1.

- [26] ATLAS, "2D Device Simulator", (SILVACO Int. Santa Clara, CA, USA, 2019).

- [27] Dhiman, P., Kavi, K.K., Ratnesh, R.K., and Kumar, A., Intern. Conf. Devc. Intel., Comp. Com. Techno. (DICCT) (2023) 1-5.

- [28] Kavi, K.K., Kiroula, K., Kumar, M., Dwivedi, A., and Mishra, R.A., IEEE Stu. Conf. Eng. Sys. (SCES), (2022) 16.

- [29] Gupta, A., Rai, A., Kumar, N., Sigroha, D., Kishore, A., Pathak, V., and Rahman, Z.U., Silicon, 14 (2022) 1005.

- [30] Gupta, V., Awasthi, H., Kumar, N., Pandey, A.K., and Gupta, A., Silicon, 14 (2022) 2989.